今天小编要和大家分享的是Allegro相关信息,接下来我将从cadence allegro 16.6,cadence,与诸位分享cadence allegro,sigrity等产品最新的科技成果和这几个方面来介绍。

Allegro相关技术文章cadence allegro 16.6

本文为大家带来cadence allegro pcb layout详细教程 。

工程师的巨大福利,首款P_C_B分析软件,点击免费领取

一、用Design Entry CIS(Capture)设计原理图

1、创建工程

file--》new--》project ;输入工程名称,指定工程放置路径;

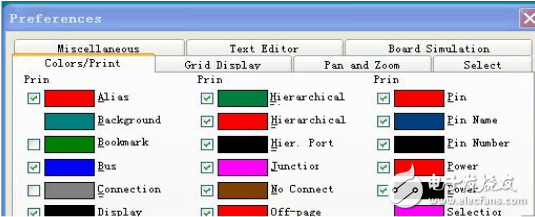

2、设置操作环境Options--》Preferencses:

颜色:colors/Print

格子:Grid Display

杂项:Miscellaneous

常取默认值

3、配置设计图纸:

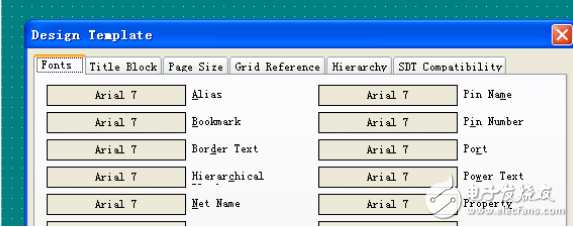

设定模板:Options--》Design Template:(应用于新图)

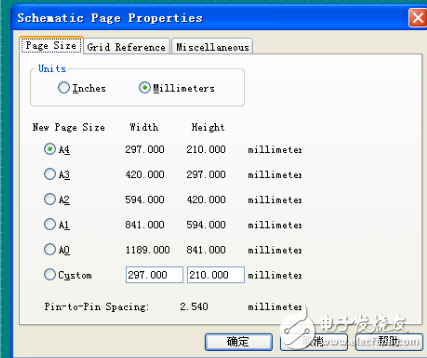

设定当前图纸Options--》Schematic Page Properities

4、创建元件及元件库

File--》New Library --》选择要添加到的工程

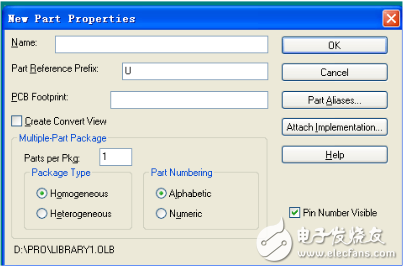

Design --》New Part.(或者在Library处右击选择New Part)

(1)Homogeneous:复合封装元件中(多个元件图组成时)每个元件图都一样(default适用于标准逻辑)

(2)Heterogeneous:复合封装元件(多个元件图组成时)中使用不一样的元件图(较适用于大元件)

一个封装下多个元件图,以View ext part(previous part)切换视图 元器件封装:

(1)place --》line 画线,用来画封装外形;

画线,用来画封装外形;

(2)place--》pin 放置管脚;放单个或多个;

放置管脚;放单个或多个;

不同类型的管脚选择的type不同;

5、绘制原理图

(1)放置电器

Place--》part ;可以从设计缓存中,活着元件库,软件自带元件库,中选择;选择Add Library增加元件库;

电源和地(power gnd)从右边工具栏中选择;

(2)连接线路 wire

bus:与wire之间必须以支线连接,并以网标(net alias)对应(wire:D0,D1.。。.D7;bus:D[0..7]) 数据总线和数据总线的引出线必须定义net alias

(3)Schematic new page (可以多张图:

单层次电路图间,以相同名称的“电路端口连接器”off-page connector连接

多层次式电路图:以方块图(层次块Hierarchical Block.。。)来代替实际电路的电路图,以相同名称Port的配对内层电路,内层电路之间可以多张,同单层连接

(4)PCB层预处理

编辑元件属性

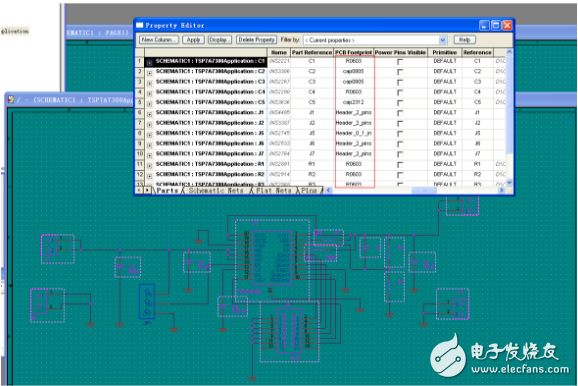

在导入PCB之前,必须正确填写元件的封装(PCB Footprint) 参数整体赋值(框住多个元件,然后Edit Properties),出现如图所示的property editer; 编辑pcb footPrint(与allegro pcb中的元器件的封装名称相一致);part Perference是网表导入allegro pcb后的元器件名称;还能进行其他属性编辑;还可添加其他需要的属性;

(6)分类属性编辑

Edit Properties--》New ColumnClass:IC(IC,IO,Discrete三类,在PCB中分类放置) 放置定义房间(Room) Edit Properties--》New ColumnRoom 添加文本和图像

添加文本、位图(Place.。。)

6、 原理图绘制的后续处理

(切换到项目管理器窗口,选中*.DSN文件,然后进行后处理————DRC检查、生成网表及元器件清单)

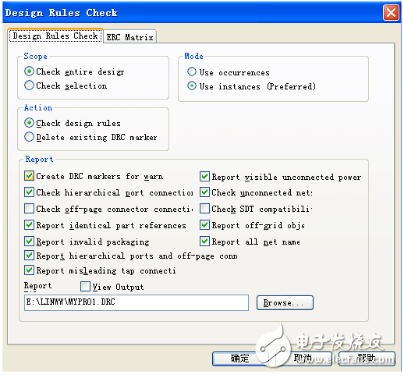

(1)设计规则检查(Tools--》Design Rules Check.。。)

Design Rules Check

scope(范围):entire(全部)/selection(所选)

Mode(模式):occurences(事件:在同一绘图页内同一实体出现多次的实体电路) instance(实体:绘图页内的元件符号) Action(动作):check design rules/delete DRC Report(报告):

Create DRC markers for warn(在错误之处放置警告标记) Check hierarchical port connection(层次式端口连接) Check off-page connector connection(平坦式端口连接) Report identical part referenves(检查重复的元件序号) Report invalid package (检查无效的封装)

Report hierarchical ports and off-page connector(列出port和off-page 连接) Check unconnected net Check SDT compatible Report all net names

(2)元件自动编号(Tools --》Annotate)

scope(范围):Update entire design/selection

Action:Incremental reference update 增长的自动编号

unconfitional reference update

reset part reference to “?” 将编号重置为“?”;

Add/delete Intersheet Reference(在分页图纸的端口的序号加上/删除图纸的编号) Reset reference numbers to begin at 1 each page原理图每个页重置编号从1开始

(3)自动更新器件或网络的属性(Tools--》Update Properties.。。)

7、生成网表

在原理图检查无误后

Tools--》Create NetLists生成网表;

二、Cadence PCB editor绘制PCB板

步骤:焊盘设计,零件封装→创建电路板,机械结构尺寸层叠结构预定义→导入网表→设定电器规则线宽线距→布局布线→布线后调整零件编号,丝印,DRC检查→设计输出gerber文件Drill文件图纸

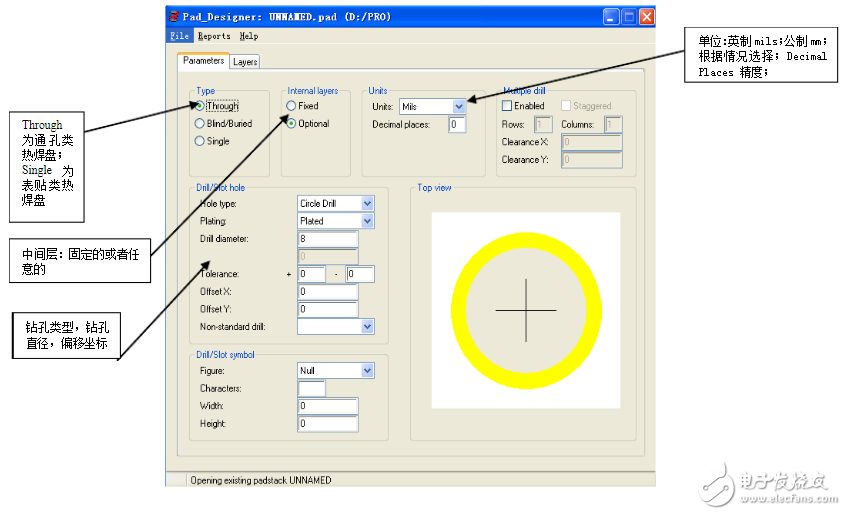

1、Cadence SPB15.7 Pad Designer画电子元器件的焊盘;

(1)File--》New创建文件

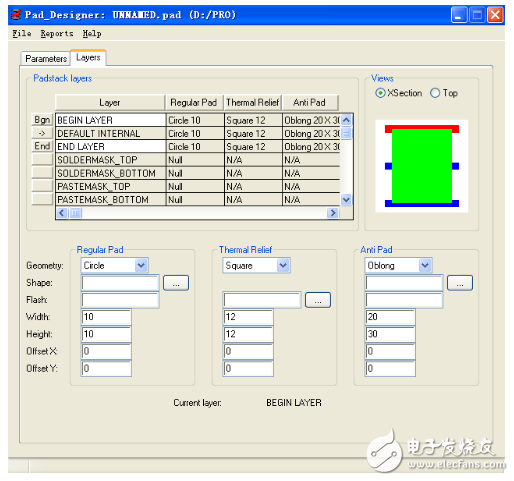

2)层的定义:BEGIN Layer(Top)层:REGULAR-PAD < THERMAL-PAD = ANTI-PAD END LAYER(同BEGIN,常用copy begin layer, then paste it)

TOP SOLDERMASK:只定义REGULAR-PAD ,大于(Begin layer层regular-pad,约为1.1~1.2倍)

BOTTOM SOLDERMASK(同Top soldermask,常用Top soldermask, then paste it)

PASTEMASK _TOP(同BEGIN,常用copy begin layer, then paste it) 设置高度,宽度,偏移坐标原点的x,y值;

(3)A:规则的焊盘可以在Geometry中选择圆形,正方形,长方形,椭圆形等; B:不规则焊盘需要导入设计好的图形;

图形通过Allegro PCB Editer设计; File --》new --》shape symbol;

设计好begin层和soldermask_top层的图形后设置放置路径setup--user preference editer选择Design_paths

Cadence PCB editor零件封装 手工建立元件(主要包含四项:

PIN;Geometry:SilkScreen/Assembly;Areas:Boundary/Height;RefDes:SilkScreen/Display)

注意:元件应放置在坐标中心位置,即(0,0)

(1)、File →new→package symbol

(2)、设定绘图区域:Setup →Drawing size →Drawing parameter.。。

设置栅格点:setup →Grids;

(3)、添加pin:选择padstack ,放置。放置前先设置方向,坐标,编号。 (4)、添加元件外形:(Geometery)

*丝印层Silkscreen:AddLine(OptionActive:package geometery;subclass:silkscreen_top) *装配外框Assembly:AddLine(OptionActive:package geometery;subclass:Assembly_top) (5)、添加元件范围和高度:(Areas)

*元件范围Boundary:Setup →Areas →package boundary.。。。

Add Line(OptionActive Class:Package geometry;subclass:Package_bound_top) *元件高度Height:Setup →Areas →package Height.。。。

Add Line(OptionActive Class:Package geometry;subclass:Package_bound_top) (6)、添加封装标志:(RefDes)LayoutLabelsResDs.。。)

*底片用封装序号(ResDes For Artwork):Pin1附近(。。.RefDes:Silkscreen_Top) *摆放用封装序号(ResDes For Placement):封装中心附近(。。.RefDes:Display_Top) *封装中心点(Body center):指定封装中心位置(Add →Text →Package Geometery:Boby_centre)

2、创建电路板

(1)、file→new→broad

(2)、基本设置(同零件封装基本设置);

(3)、绘制外框(outline):Options→Board geometry:outline

(4)、添加定位孔

(5)、倾斜拐角:(dimension chamfer)

(6)、设定走线区域:shape→polygon.。.option route keepin:all

(7)、设置摆放元件区域:Editz-copy shape.。.options package keepin:all;

(8)、设置不可摆放元件区域:setup→areas→package keepout

(9)、设定不可走线区域:setup→areas route keepout

3、设置约束规则

(1)、Allegro中设置约束规则(Setup→Constraints.。)Spacing Rules和 Physical Rules

(2)、设置默认规范。。.setup→constraints →set standard value

(3)、设置和赋值高级间距规范 : 设定间距规范值:set value

设定间距的Type属性:Edit→Properties

(4)、设置和赋值高级物理规范 :(基本同上) 设定物理规范值:

(5)、建立设计规范的检查(setup constraits.。。 )

4、导入网表

File→ Import →logic;

5、布局布线

1、手动摆放元件:Placemanually.。。。。。

查看元件属性:DisplayElemant;;FindComps;单击要查看属性的元件

2、自动摆放元件:PlaceQuick Place.。。。。。 3、随机摆放:EditMove.。。

4、自动布局:Place auto Place 网格:Top Grid.。

设置元件进行自动布局的属性:EditProperties Find 。.more.。

5、设定Room:

设定Room:add rectangle;options board geometry op room 给Room定义名字;Add ext;options board geometry op room

定义该Room所限制的特性和定义某些元件必须放置在该Room中:

定义Room所限制的特性:Edit Properties;选中Room;Edit properties;Room_type=hard(指定room的元件必须放Room中)

定义放入Room中的元件:Edit properties;

6、摆放调整(Move、Mirror、Spin)

7、交换(swap)(配合原理图使用,比较少用)

8、未摆放元件报表(ToolReport.。。)

9、已摆放元件报表(ToolReport.。。)

6、Allegro 产生钻孔文件

(1)、设置钻孔参数 Manufacture-》NC-》NC Parameters Paraeter file : 参数文件所在路径(默认nc_param.txt) Output file: 输出文件内容设置(默认设置就ok) Exellon format钻孔文件输出使用的格式

format :2.3

(2表示小数点前面为2位,3表示小数点后面为3位) offset : 输出的坐标值和pcb的坐标值的差距 coordinates :

绝对坐标和增量坐标 Output units :

输出的那位英制或公制 leading

(2)、产生钻孔文件 Manufacture-》NC-》NC Drill.。。 root file name : 钻孔文件的名字和路径

Scale factor : 钻孔比例因子(建议不要设置) Tool sequence : 钻孔工具递增或递减

Auto tool select :自动选择工具 Drilling :

Layer pair (全为通孔) By layer (有盲孔或埋孔)

(3)Drill、 产生过孔文件

(4)View Log: 查看钻孔记录 可能出现的警告: WARNING: Design precision is greater than that of the drill output file data. Data rounding errors are very possible. 解决方案:

Manufacture-》NC-》NC Parameters-》Exellon format-》format : 3.6(报错原因过孔精度不足,提高过孔精度)

WARNING: This design contains 1 slot holes that can NOT be drilled. They can be processed by NC routing instead. 解决方案: Manufacture-》NC-》NC route(产生不规则钻孔,警告可忽略)产生rou文件 (5)产生钻孔表 Manufacture-》NC-》NC Legend

相关资料下载推荐>>>>>>>>利用Cadence Allegro进行PCB级的信号完整性仿真

关于Allegro就介绍完了,您有什么想法可以联系小编。