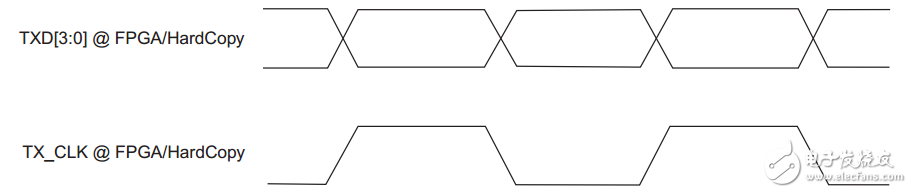

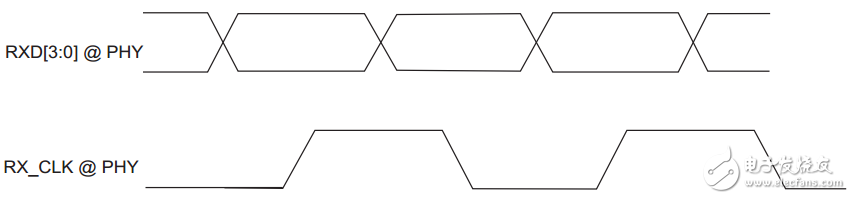

PHY内部会调整TX_CLK,使之能够稳定采样TXD。数据接收方向,由于RX_CLK由PHY提供,PHY芯片直接产生与数据中心对齐的时钟信号。RXD和RX_CLK信号波形如图。

可见,使PHY芯片工作在延迟模式下时,FPGA单不需要添加额外的逻辑来保证稳定采样。发送方向直接将数据驱动时钟作为TX_CLK信号发送,接收方向直接利用RX_CLK对RXD信号采样。

四、系统设计方案

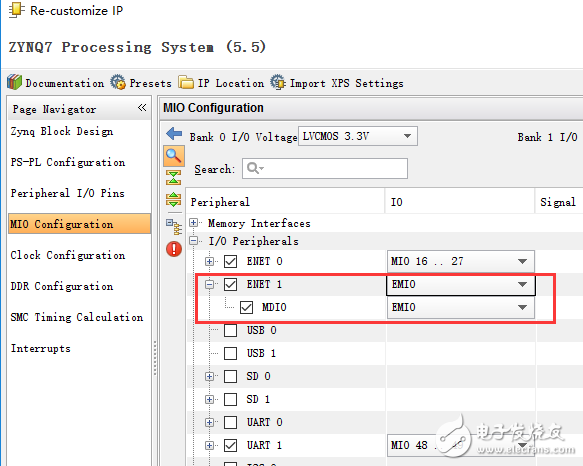

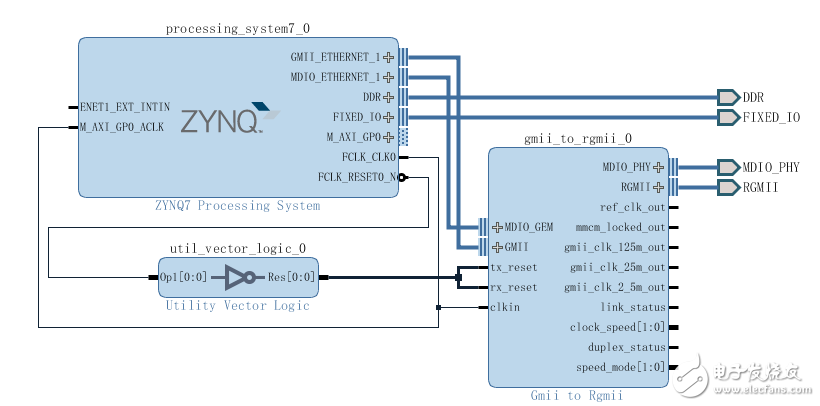

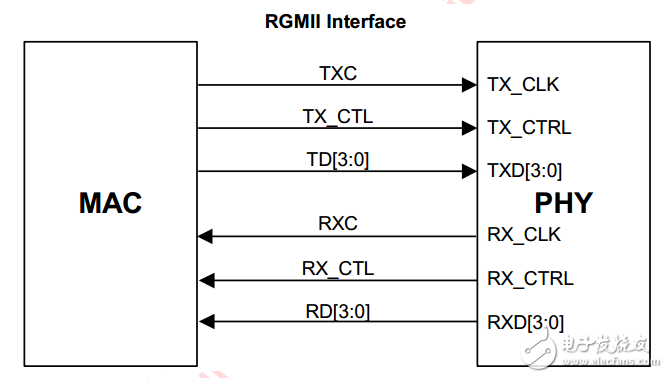

本文使用ZYNQ内部的MAC控制器实现数据链路层功能。但由于其接口为GMII,需要用到GMII_to_RGMII IP Core转换接口逻辑。上层网络协议则通过LWIP开源协议栈完成。首先配置ZYNQ IP,使能ENET1并以EMIO方式引出。

系统硬件结构如图:

五、I/O 时序约束

在较高速设计场合下,输入输出接口部分很容易出现数据采样不稳定的现象。这时候就要通过Input delay,output delay约束以及STA来分析设计是否满足稳定采样需求。input/output delay是指数据相对于时钟的延迟,只有设置好上述两个数值,综合工具才会往正确的方向优化并给出合理的时序报告。

FPGA与RGMII接口的PHY芯片之间的时序关系按照数据接口同步和数据采样方式属于源同步DDR采样。input delay约束对应接收方向,时序关系是中心对齐。output delay约束对应发送方向,时序关系是边沿对齐。前者由于很多时候不知道上游器件Tcko信息,会使用示波器测量有效数据窗口来计算。而后者因为是边沿对齐,通过示波器测量抖动窗口并使用skew based method计算。这部分笔者还没有亲身实践过,若有误欢迎指出。

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。