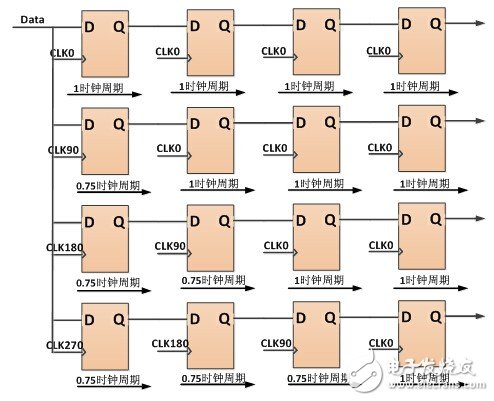

本方案采用同频多相的时钟采样方法,具体实现过程利用PLL产生4个时钟频率相同,相位相差90度的时钟,分别为clk0、clk90、clk180、clk270,这四个时钟输出完全同步,利用4个时钟对数据进行采样,以获得4倍过采样的效果,具体的实现过程如下图所示:

在数据时钟恢复时,将到来的数据分别输入到四个触发器,分别用4个不同的相位进行采样,要注意保证从输入引脚到四个触发器的延迟基本一致。

第一列触发器的触发分别由时钟CLK0、CLK90、CLK180、CLK270的上升沿触发,按照这样的方式来触发就可以得到四个数据采样点。这样就将原始时钟周期分成了四个单独的90度的区域,如果系统时钟为200MHz,上图所示的电路就相当于产生了800MHz 的采样速率。

仅通过一阶的触发器,输出的采样数据存在亚稳态的问题,因此需对采样点作进一步的处理。这里可将四个采样点通过进一步的触发,除掉亚稳态的问题,从而使采样点移到下一个相同的时钟域。通常,亚稳态的去除要经过两三级的处理,这就使得在有效数据输出前会有数位无效的数据,在数据采样的第一个阶段,电路检测数据线上数据的传输。当检测到有数据传输时,对传输数据的有效性进行确认。确认数据有效后,输出高电平来指示采样点有数据传输。

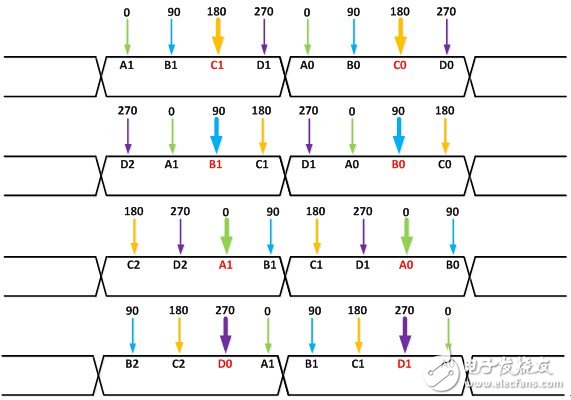

因为最终有四个输出,所以需要一个复用器来选择数据。发送数据与采样时钟的对应关系如上图所示,其对应关系分为4种情况,每种情况下对应一个最佳的采样时钟,系统通过对数据边沿位置信息的判断,来确定哪路时钟为最佳采样时钟,并利用复用器从选定的时钟域中选择数据位,例如检测电路确定从时钟域A中采样的数据有效,那么将时钟域A中采样的数据通过输出端输出。

3 结束语:

通过对纯数字电路的CDR电路,在没有硬核的支持下,完成了FPGA上SERDES的接口设计,并通过实验的传输测试,在HR03的FPGA上,可完成100~200Mbps的数据传输。

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。