阻抗的变化必然影响信号的反射。在充电的开始一段时间,阻抗很小,小于传输线的特性阻抗,将发生负反射,反射回源端A点的信号将产生下冲。随着电容阻抗的增加,反射逐渐过渡到正反射,A点的信号经过一个下冲会逐渐升高,最终达到开路电压。

因此电容负载使源端信号产生局部电压凹陷。精确波形和传输线的特性阻抗、电容量、信号上升时间有关。

对于接收端,很明显,就是一个RC充电电路,不是很严谨,但是和实际情况非常相似。电容两端电压,即B点电压随RC充电电路的时间常数呈指数增加(基本电路原理)。因此电容对接收端信号上升时间产生影响。

RC充电电路的时间常数为  这是B点电压上升到电压终值的

这是B点电压上升到电压终值的  即37%所需的时间。B点电压10%~90%上升时间为

即37%所需的时间。B点电压10%~90%上升时间为

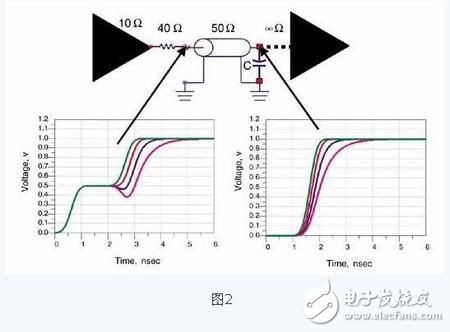

如果传输线特性阻抗为50欧姆,电容量10pF,则10~90充电时间为1.1ns。如果信号上升时间小于1.1ns,那么B点电压上升时间主要由电容充电时间决定。如果信号上升时间大于1.1ns,末端电容器作用是使上升时间进一步延长,增加约1.1ns(实际应比这个值小)。图2显示了终端电容负载对驱动端和接受端产生影响的示意图,放在这里,让大家能有个感性的认识。

至于信号上升时间增加的精确值是多少,对于电路设计来说没必要,只要定性的分析,有个大致的估算就可以了。因为计算再精确也没实际意义,电路板的参数也不精确!对于设计者来说,定性分析并了解影响,大致估算出影响在那个量级,能给电路设计提供指导就可以了,其他的事软件来做吧。举个例子,如果信号上升时间1ns,电容使信号上升时间增加远小于1ns,比如0.2 ns,那么这么一点点增加可能不会有什么影响。如果电容造成的上升时间增加很多,那可能就会对电路时序产生影响。那么多少算很多?看看电路的时序余量吧,这涉及到电路的时序分析和时序设计。

总之接收端电容负载的影响有两点:

1、 使源端(驱动端)信号产生局部电压凹陷。

2、 接收端信号上升时间延长。

在电路设计中这两点都要考虑。

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。