今天小编要和大家分享的是12进制计数器,计数器相关信息,接下来我将从12进制计数器设计方案汇总(五款模拟电路设计原理及程序分享),《4.同步二进制加法计数器.pptx》这几个方面来介绍。

《4.同步二进制加法计数器.pptx》

本文为大家带来五种不同的12进制计数器设计方案。

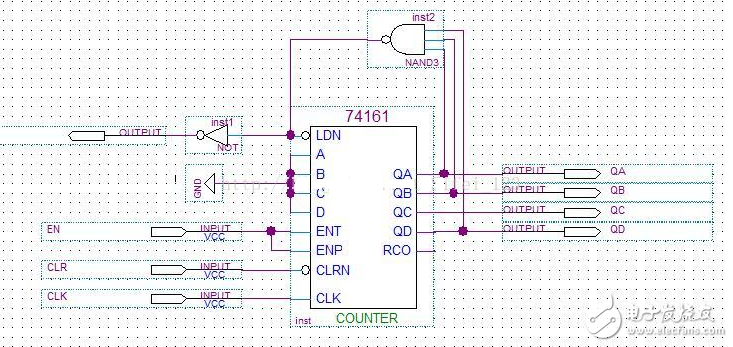

12进制计数器设计方案一:用74161设计十二进制计数器

1.74161为十六进制计数器,设计十二进制计数器时1片就可以满足要求。

2.新建BDF文件及保存工程同前篇。

3.将所需要的元器件和引脚拖入区域内并完成连接,如图1所示

图1 十二进制计数器连接图

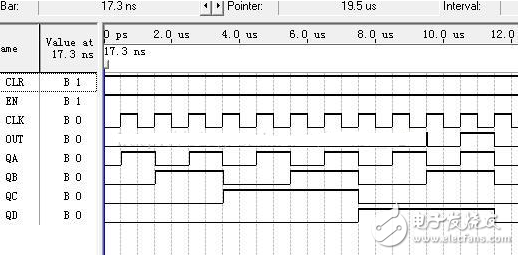

4.建立VWF文件,仿真后得到结果如图2

仿真波形图

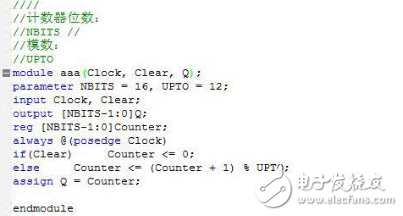

12进制计数器设计方案二:用verilog语言实现十二进制计数器

程序代码

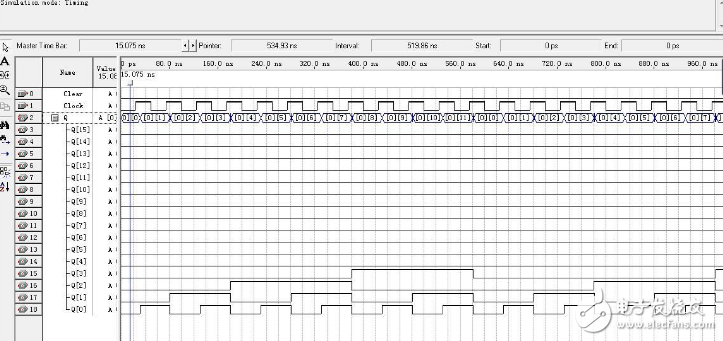

仿真结果

12进制计数器设计方案三:异步十二进制加减法计数器设计1

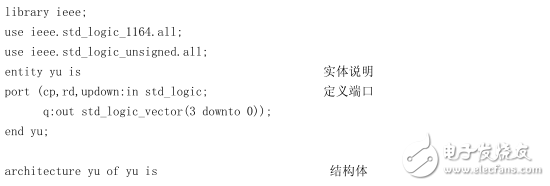

VHDl设计思路

设计中,CP 是时钟输入端,下降沿有效;Rd 为清零控制端,低电平有效; updown 为计数方式控制端,updown=“1”时作加法计数,updown=“0”时作减法计数。在计数工作之前,先由Rd 给一个清零信号,使四个数据输入值都为“0”。y3,y2,y1,y0 为四个数据输出端,这就实现了异步清零。当Rd=“1”时,计数器进行加法计数,即从“0000”依次计数到“1011”,当updown= “0”,updown=“1”,Rd=“1”时,计数器进行减法计数。

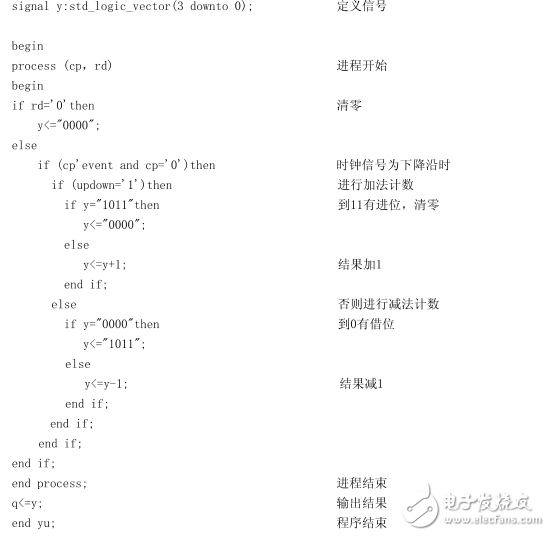

程序设计

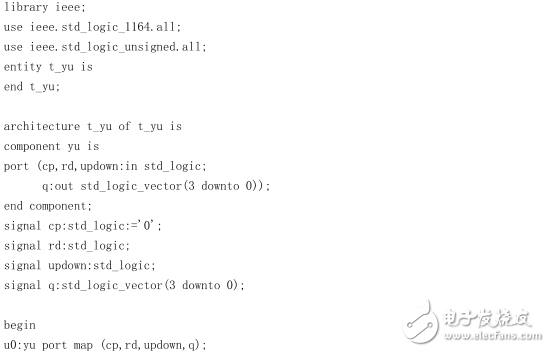

仿真测试程序

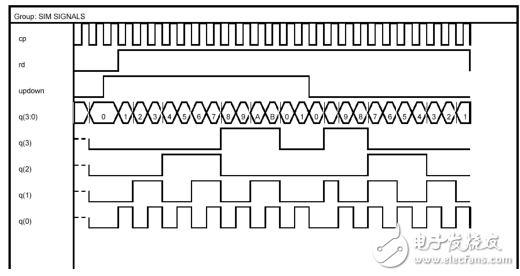

仿真图

12进制计数器设计方案四:异步十二进制加减法计数器设计2

VHDl设计思路

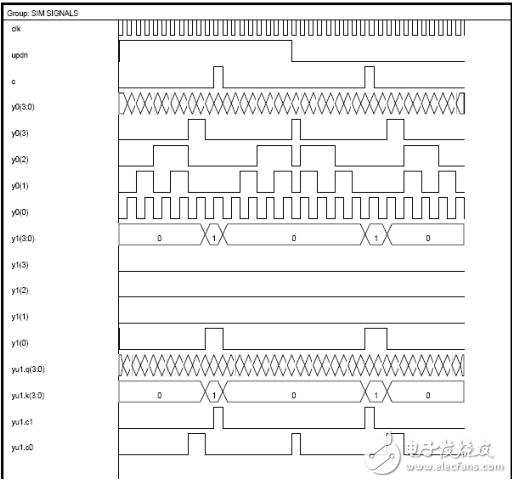

设计中,clk 是时钟输入端,上升沿有效;updn 为计数方式控制端,updn=“1”时作加法计数,updn=“0”时作减法计数; c 是进位/借位输出端; c0 为个位最高位输出。在计数工作之前,个位q 和十位k 全部置0。个位由时钟上升沿触发加/减1,十位由个位的进位/借位触发,从而实现十位的变化,即异步可逆计数。当updown=“1”时,计数器进行加法计数,个位从“0”依次计数到“9”,进位,十位由“0”到“1”,当计数到11时清零;同理,当updown=“0”时,计数器进行减法计数。

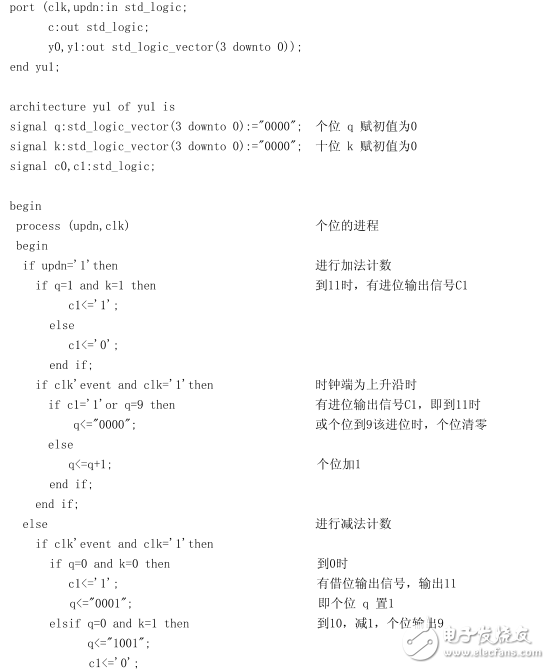

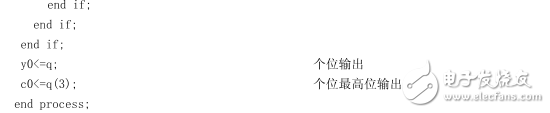

程序设计

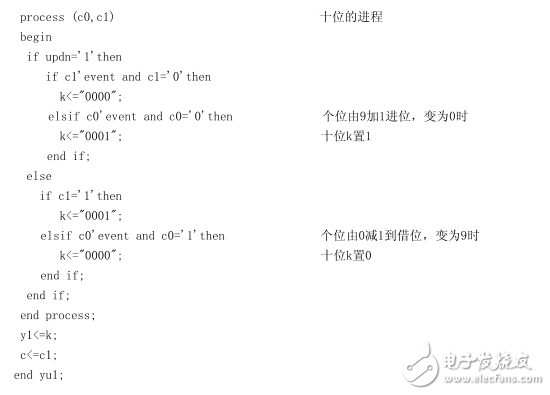

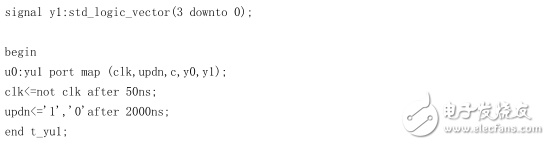

仿真验证程序

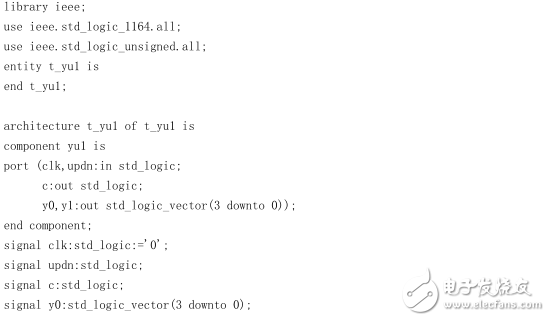

仿真图

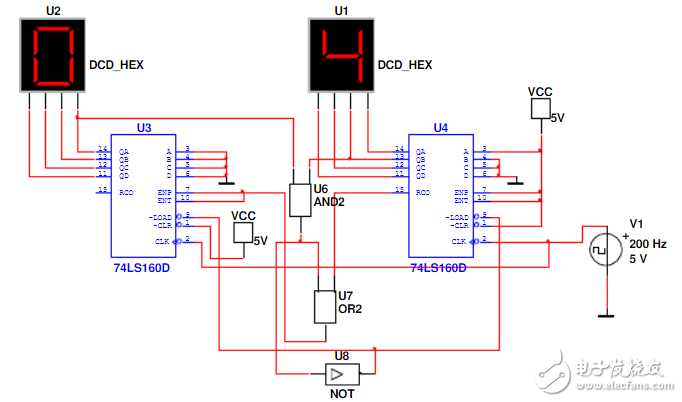

12进制计数器设计方案五:应用两片74LS160设计十二进制计数器

两芯片之间级联;把作高位芯片的进位端与下一级up端连接这是由两片74LS160连接而成的12进制计数器,低位是连接成为一个十进制计数器,它的clk端接的是低位的进位脉冲。高位接成了十进制计数器。当输出端为1010 的时候在下个时钟的上升沿把数据置数成0000 这样就形成了进制计数器,连个级联就成为了12进制计数器,分别可以作为秒和分记时。

关于12进制计数器,计数器就介绍完了,您有什么想法可以联系小编。