今天小编要和大家分享的是EDA,IC设计相关信息,接下来我将从基于高速DSP电路的PCB抗干扰设计,基于dsp的高速pcb抗干扰设计.pdf这几个方面来介绍。

EDA,IC设计相关技术文章基于高速DSP电路的PCB抗干扰设计

高速系统中,噪声干扰的产生是第一影响因素,高频电路还会产生辐射和冲突,而较快的边缘速率则会产生振铃、反射和串扰。如果不考虑高速信号布局布线的特殊性,设计出的电路板将不能正常工作。因此PCB板的设计成功是DSP电路设计过程中非常关键的一个环节。

1 传输线效应

1.1信号完整性

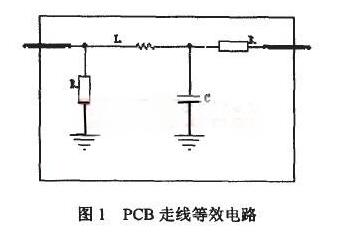

信号完整性主要有反射、振铃、地弹和串扰等现象。PCB板上的走线可等效为图1所示的串联和并联的电容、电阻和电感结构。串联电阻的典型值0.25D./R-4)。55DJft,并联电阻阻值通常很高。将寄生电阻、电容和电感加到实际的PCB连线中之后,连线上的最终阻抗称为特征阻抗zo。

如果传输线和接收端的阻抗不匹配,这就会引起信号的反射和振荡。

布线的几何形状,不正确的线端接,经过连接器的传输及电源平面的不连续等因素的变化均会导致反射。过冲和下冲是信号在电平上升沿和下降沿变化时产生的,会在瞬间产生高于或低于平稳电平的毛刺,容易损坏器件。信号的振铃和环绕振荡分别是由线上不恰当的电感和电容所应起的。振铃可以通过适当的端接予以减小。

当电路中有大的电流涌动时会引起地弹,若有一个较大的瞬态电流在芯片与板的电源平面流过,芯片封装与电源平面间的寄生电感和电阻就会引发电源噪声。串扰是两条信号线之间的耦合问题,信号线之间的互感和互容导致了线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

1.2 解决办法

要解决常见的问题需要采取的一些措施:

电源层对电流方向不限制,返回线可沿着最小阻抗即与信号线最接近的路径走。这就可能使电流回路最小,而这将是技术系统首选的方法。但是电源层不排除线路杂波,不注意电源分布路径,所有系统均会产生噪声造成错误。因此需要特殊的滤波器,由旁路电容实现。一般一个l虾到lOp.F的电容放在板上电源输入端,而0.01p.F至U0.1心的电容放在板上每个有源器件的电源、地的管脚之间。旁路电容的作用就像滤波器,大电容(10aF)放在电源输入端,滤除板外产生的低频(60Hz)噪声,板上有源器件产生的噪声在100MHz或更高的频率下会产生谐波,放在每个芯片之间的旁路电容通常比放在板上电源输入端的电容小得多。